## PRELIMINARY

## Am53C974

# PCSCSI™ Bus Mastering Fast SCSI Controller for PCI Systems

## **DISTINCTIVE CHARACTERISTICS**

#### **PCI** Features

- Compatible with PCI Specification Revision 2.0

- Direct glueless interface to 33 MHz, 32-bit PCI bus

- Bus Mastering DMA engine (32-bit address/data)

- 132 Mbyte/s burst DMA transfer rate

- Support for Scatter-Gather DMA data transfers

- 96-byte DMA FIFO for low bus latency

#### **SCSI Features**

- Fast 8-bit SCSI-2 10 Mbyte/s synchronous or 7 Mbyte/s asynchronous data transfer rate

- On-chip state machine to control the SCSI sequences in hardware

- Patented programmable GLITCH EATER™ Circuitry on REQ and ACK and data inputs

- Programmable Active Negation on REQ, ACK and data outputs

- Integrated industry standard Fast SCSI-2 core

- Single-Ended 48 mA outputs to drive the SCSI bus directly

#### General Features

- Complete software driver support for all major PC operating systems

- Plug-In and software compatible with AMD's PCI product family of SCSI and Ethernet controllers

- Hooks in silicon and software to enable disk drive spin down for power savings

- Fully static design for low frequency and power operation

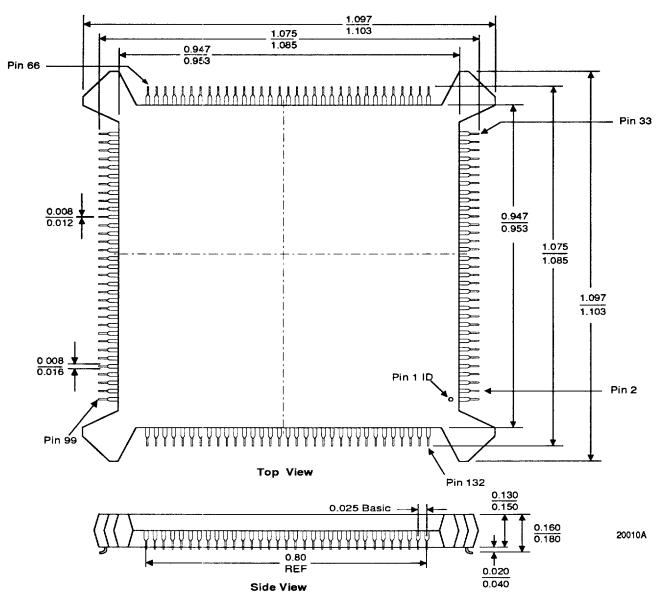

- 132-pin PQFP package

- State of the art Am386® submicron CMOS process technology

#### **GENERAL DESCRIPTION**

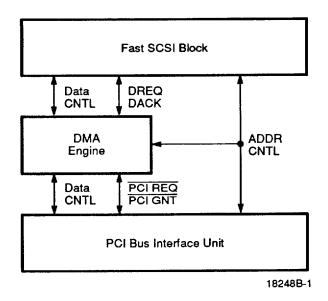

The Am53C974, PCscsi, is a high-performance Fast SCSI controller with a glueless interface to the PCI local bus. The Am53C974 integrates a 32-bit bus mastering DMA engine with an industry standard Fast SCSI-2 block. The DMA engine and accompanying 96 byte DMA FIFO allow 32-bit burst data transfers across the high bandwidth PCI bus at speeds of up to 132 Mbyte/s. Full support for scatter-gather DMA transfers optimize performance in multi-tasking system applications.

The Am53C974's on-chip state machine controls SCSI bus sequences in hardware and is coupled with the bus mastering DMA engine to eliminate the need for an on-chip RISC processor. This results in a smaller die size giving the Am53C974 superior price/performance versus competitive offerings. For more detailed information refer to the technical manual, PID #18264B.

AMD supports the Am53C974 with a total system solution which includes:

A full suite of licensable SCSI drivers and utilities fully tested under the following operating system environments:

> DOS 5.0 – 6.0 Windows 3.1 Windows NT OS/2 2.x Netware 3.x, 4.x SCO Unix 3.2.4, ODT 2.0

- An INT13h Compatible SCSI ROM BIOS

- ASPI Compatibility

- Complete hardware reference design kit

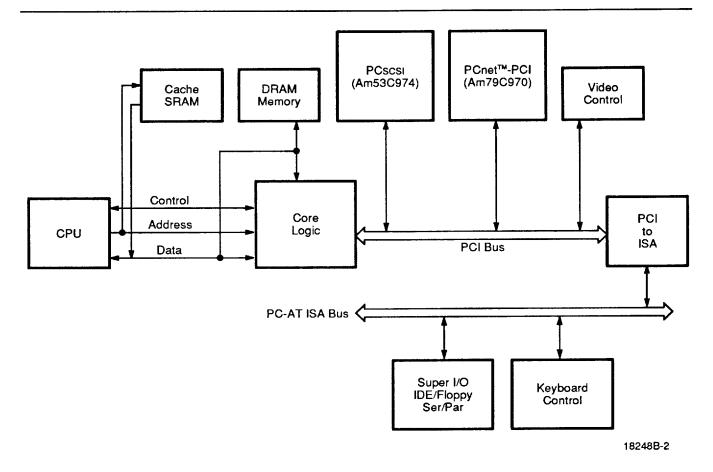

The Am53C974 is part of AMD's PCI product family of plug-in and software compatible SCSI and Ethernet controllers. This product compatibility ensures a low cost system upgrade path and lower motherboard manufacturing costs.

This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended to help you to evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice.

Publication# 18248 Rev. B Amendment/0 issue Date: November 1993

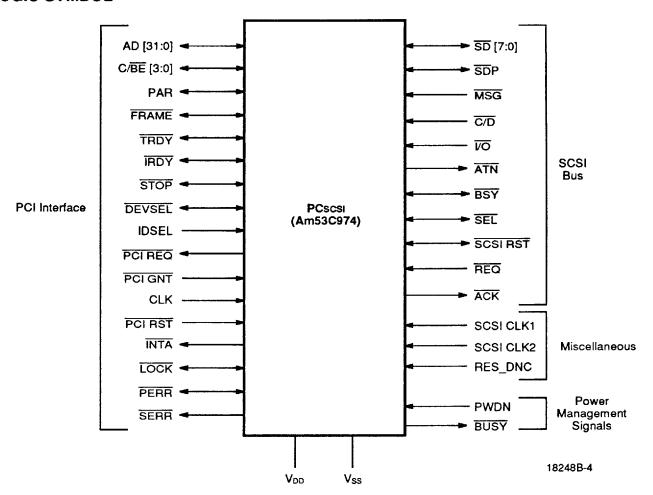

## **BLOCK DIAGRAM**

Am53C974 in a PCI System

## **RELATED AMD PRODUCTS**

| Part No.                                                 | Description                                                 |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| Am33C93A                                                 | Synchronous SCSI Controller                                 |  |  |  |

| Am386®                                                   | High-Performance 32-Bit Microprocessor                      |  |  |  |

| Am486™                                                   | High-Performance 32-Bit Microprocessor                      |  |  |  |

| Am53C94/96                                               |                                                             |  |  |  |

| Am53CF94/96                                              | Enhanced Fast SCSI-2 Controller                             |  |  |  |

| Am79C960                                                 | PCnet-ISA Single-Chip Ethernet Controller                   |  |  |  |

| Am79C961                                                 | PCnet-ISA+ Single-Chip Ethernet Controller                  |  |  |  |

| Am79C965 PCnet-32 Single-Chip 32-Bit Ethernet Controller |                                                             |  |  |  |

| Am79C970                                                 | PCnet-PCI Single-Chip Ethernet Controller for PCI Local Bus |  |  |  |

| Am85C30                                                  | Enhanced Serial Communication Controller                    |  |  |  |

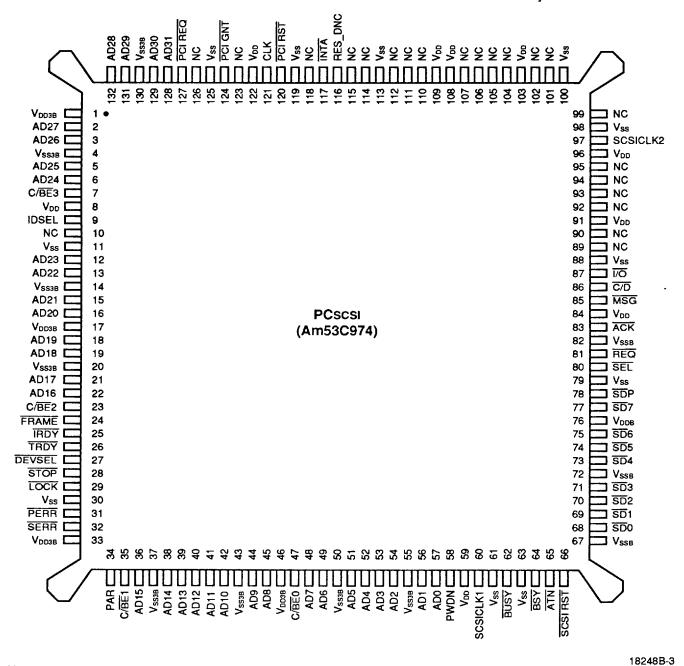

## CONNECTION DIAGRAM

### **Top View**

#### Notes:

Pin 1 is marked for orientation.

NC = Not connected; connection of an NC pin may cause a malfunction or incompatibility with other products.

RES\_DNC = Reserved\_DO NOT CONNECT.

## **QUICK REFERENCE PIN DESCRIPTIONS**

| Pin Name          | Pin Type      | Description                  |  |  |

|-------------------|---------------|------------------------------|--|--|

| PCI               |               |                              |  |  |

| AD [31:00]        | IN/OUT        | Address/Data Bus             |  |  |

| C/BE [3:0]        | IN/OUT        | Command/Byte Enable signals  |  |  |

| PAR               | IN/OUT        | Parity Signal                |  |  |

| FRAME             | IN/OUT        | Cycle Frame                  |  |  |

| TRDY              | IN/OUT        | Target Ready                 |  |  |

| IRDY              | IN/OUT        | Initiator Ready              |  |  |

| STOP              | IN/OUT        | Stop                         |  |  |

| LOCK              | IN/OUT        | Lock                         |  |  |

| IDSEL             | IN            | Initialization Device Select |  |  |

| DEVSEL            | IN/OUT        | Device Select                |  |  |

| PCIREQ            | OUT           | PCI Request                  |  |  |

| PCIGNT            | IN            | PCI Grant                    |  |  |

| CLK               | in            | PCI Clock                    |  |  |

| PCIRST            | IN            | PCI Reset                    |  |  |

| PERR              | IN/OUT        | Parity Error                 |  |  |

| SERR              | OUT           | System Error                 |  |  |

| INTA              | OUT           |                              |  |  |

|                   | 1 001         | Interrupt                    |  |  |

| SCSI Interface    | Lavour        | 00010                        |  |  |

| SD [7:0]          | IN/OUT        | SCSI Data                    |  |  |

| SDP               | IN/OUT        | SCSI Data Parity             |  |  |

| MSG               | IN            | Message                      |  |  |

| <u>C/D</u>        | IN            | Command/Data                 |  |  |

| <u>VO</u>         | IN            | Input/Output                 |  |  |

| ATN               | OUT           | Attention                    |  |  |

| BSY               | IN/OUT        | Busy                         |  |  |

| SEL               | IN/OUT        | Select                       |  |  |

| SCSI RST          | IN/OUT        | SCSI Bus Reset               |  |  |

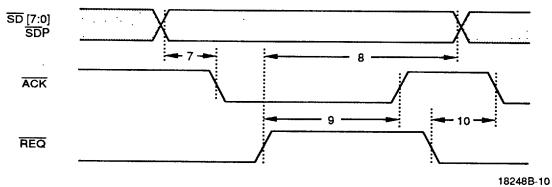

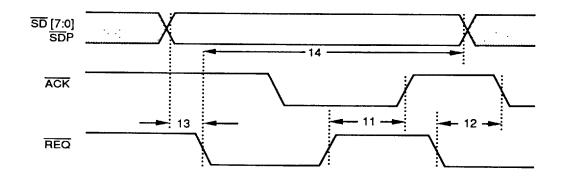

| REQ               | IN            | Request                      |  |  |

| ACK               | OUT           | Acknowledge                  |  |  |

| Miscellaneous     |               |                              |  |  |

| SCSI CLK1         | IN            | SCSI Core Clock              |  |  |

| SCSI CLK2         | IN            | Chip Reset Clock             |  |  |

| RES_DNC           | IN            | Reserved, DO NOT CONNECT     |  |  |

| Power Management  |               |                              |  |  |

| PWDN              | IN            | Power Down Indicator         |  |  |

| BUSY              | OUT           | SCSI Bus Activity Pin        |  |  |

| Power Supply      |               |                              |  |  |

| V <sub>DD</sub>   | +5 V          |                              |  |  |

| V <sub>SS</sub>   | GND           |                              |  |  |

| V <sub>DOB</sub>  | +5 V (Buffer) |                              |  |  |

| V <sub>SSB</sub>  | GND (Buffer)  |                              |  |  |

| V <sub>DD3B</sub> | +5 V (PCI)    |                              |  |  |

| V <sub>SS3B</sub> | GND (5 V PCI) |                              |  |  |

## **PQFP PIN DESIGNATIONS**

## **Listed by Pin Number**

| Pin No. | Pin Name          | Pin No. | Pin Name          | Pin No. | Pin Name         | Pin No. | Pin Name          |

|---------|-------------------|---------|-------------------|---------|------------------|---------|-------------------|

| 1       | V <sub>DD3B</sub> | 34      | PAR               | 67      | V <sub>SSB</sub> | 100     | Vss               |

| 2       | AD27              | 35      | C/BE1             | 68      | SD0              | 101     | NC                |

| 3       | AD26              | 36      | AD15              | 69      | SD1              | 102     | NC                |

| 4       | V <sub>SS3B</sub> | 37      | V <sub>SS38</sub> | 70      | SD2              | 103     | $V_{DD}$          |

| 5       | AD25              | 38      | AD14              | 71      | SD3              | 104     | NC                |

| 6       | AD24              | 39      | AD13              | 72      | V <sub>SSB</sub> | 105     | NC                |

| 7       | C/BE3             | 40      | AD12              | 73      | SD4              | 106     | NC                |

| 8       | V <sub>DD</sub>   | 41      | AD11              | 74      | SD5              | 107     | NC                |

| 9       | IDSEL             | 42      | AD10              | 75      | SD6              | 108     | $V_{DD}$          |

| 10      | NC                | 43      | V <sub>SS3B</sub> | 76      | V <sub>DDB</sub> | 109     | $V_{DD}$          |

| 11      | $V_{SS}$          | 44      | AD9               | 77      | SD7              | 110     | NC                |

| 12      | AD23              | 45      | AD8               | 78      | SDP              | 111     | NC                |

| 13      | AD22              | 46      | V <sub>DD3B</sub> | 79      | $V_{SS}$         | 112     | NC                |

| 14      | V <sub>SS3B</sub> | 47      | C/BE0             | 80      | SEL              | 113     | $V_{SS}$          |

| 15      | AD21              | 48      | AD7               | 81      | REQ              | 114     | NC                |

| 16      | AD20              | 49      | AD6               | 82      | V <sub>SSB</sub> | 115     | NC                |

| 17      | $V_{\text{DD3B}}$ | 50      | V <sub>SS3B</sub> | 83      | ACK              | 116     | RES_DNC           |

| 18      | AD19              | 51      | AD5               | 84      | $V_{DD}$         | 117     | INTA              |

| 19      | AD18              | 52      | AD4               | 85      | MSG              | 118     | NC                |

| 20      | V <sub>SS3B</sub> | 53      | AD3               | 86      | C/D              | 119     | Vss               |

| 21      | <b>A</b> D17      | 54      | AD2               | 87      | 1/0              | 120     | PCIRST            |

| 22      | AD16              | 55      | V <sub>SS3B</sub> | 88      | V <sub>ss</sub>  | 121     | CLK               |

| 23      | C/BE2             | 56      | AD1               | 89      | NC               | 122     | $V_{DD}$          |

| 24      | FRAME             | 57      | <b>A</b> D0       | 90      | NC               | 123     | NC                |

| 25      | ĪRDY              | 58      | PWDN              | 91      | V <sub>DD</sub>  | 124     | PCI GNT           |

| 26      | TRDY              | 59      | $V_{DD}$          | 92      | NC               | 125     | Vss               |

| 27      | DEVSEL            | 60      | SCSICLK1          | 93      | NC               | 126     | NC                |

| 28      | STOP              | 61      | Vss               | 94      | NC               | 127     | PCI REQ           |

| 29      | LOCK              | 62      | BUSY              | 95      | NC               | 128     | AD31              |

| 30      | Vss               | 63      | Vss               | 96      | V <sub>DD</sub>  | 129     | AD30              |

| 31      | PERR              | 64      | BSY               | 97      | SCSICLK2         | 130     | V <sub>SS3B</sub> |

| 32      | SERR              | 65      | ATN               | 98      | Vss              | 131     | AD29              |

| 33      | V <sub>DD3B</sub> | 66      | SCSI RST          | 99      | NC               | 132     | AD28              |

NC = No Connect

RES\_DNC = Reserved\_DO NOT CONNECT.

## **PQFP PIN DESIGNATIONS**

## **Listed by Pin Name**

| Pin Name | Pin No. | Pin Name   | Pin No. | Pin Name        | Pin No. | Pin Name          | Pin No. |

|----------|---------|------------|---------|-----------------|---------|-------------------|---------|

| ACK      | 83      | ATN        | 65      | NC              | 112     | V <sub>DD</sub>   | 91      |

| AD0      | 57      | BSY        | 64      | NC              | 114     | V <sub>DD</sub>   | 96      |

| AD1      | 56      | BUSY       | 62      | NC              | 115     | V <sub>DD</sub>   | 103     |

| AD2      | 54      | C/BE0      | 47      | NC              | 118     | V <sub>DD</sub>   | 108     |

| AD3      | 53      | C/BE1      | 35      | NC              | 123     | V <sub>DD</sub>   | 109     |

| AD4      | 52      | C/BE2      | 23      | NC              | 126     | V <sub>DD</sub>   | 122     |

| AD5      | 51      | C/BE3      | 7       | PAR             | 34      | V <sub>DD3B</sub> | 1       |

| AD6      | 49      | C/D        | 86      | PCI GNT         | 124     | V <sub>DO3B</sub> | 17      |

| AD7      | 48      | CLK        | 121     | PCI REQ         | 127     | V <sub>DD3B</sub> | 33      |

| AD8      | 45      | DEVSEL     | 27      | PCI RST         | 120     | V <sub>DD3B</sub> | 46      |

| AD9      | 44      | FRAME      | 24      | PERR            | 31      | $V_{DDB}$         | 76      |

| AD10     | 42      | <u>1/O</u> | 87      | PWDN            | 58      | V <sub>SS</sub>   | 11      |

| AD11     | 41      | IDSEL      | 9       | REQ             | 81      | V <sub>ss</sub>   | 30      |

| AD12     | 40      | INTA       | 117     | RES_DNC         | 116     | V <sub>ss</sub>   | 61      |

| AD13     | 39      | IRDY       | 25      | SCSIRST         | 66      | V <sub>SS</sub>   | 63      |

| AD14     | 38      | LOCK       | 29      | SCSICLK1        | 60      | V <sub>SS</sub>   | 79      |

| AD15     | 36      | MSG        | 85      | SCSICLK2        | 97      | Vss               | 88      |

| AD16     | 22      | NC         | 10      | SD0             | 68      | V <sub>SS</sub>   | 98      |

| AD17     | 21      | NC         | 89      | SD1             | 69      | Vss               | 100     |

| AD18     | 19      | NC         | 90      | SD2             | 70      | V <sub>ss</sub>   | 113     |

| AD19     | 18      | NC         | 92      | SD3             | 71      | Vss               | 119     |

| AD20     | 16      | NC         | 93      | SD4             | 73      | V <sub>ss</sub>   | 125     |

| AD21     | 15      | NC         | 94      | SD5             | 74      | V <sub>SS3B</sub> | 4       |

| AD22     | 13      | NC         | 95      | SD6             | 75      | V <sub>SS38</sub> | 14      |

| AD23     | 12      | NC         | 99      | SD7             | 77      | V <sub>SS3B</sub> | 20      |

| AD24     | 6       | NC         | 101     | SDP             | 78      | V <sub>SS3B</sub> | 37      |

| AD25     | 5       | NC         | 102     | SEL             | 80      | V <sub>SS38</sub> | 43      |

| AD26     | 3       | NC         | 104     | SERR            | 32      | V <sub>SS38</sub> | 50      |

| AD27     | 2       | NC         | 105     | STOP            | 28      | V <sub>SS38</sub> | 55      |

| AD28     | 132     | NC         | 106     | TRDY            | 26      | V <sub>SS3B</sub> | 130     |

| AD29     | 131     | NC         | 107     | V <sub>DD</sub> | 8       | V <sub>SSB</sub>  | 67      |

| AD30     | 129     | NC         | 110     | V <sub>DD</sub> | 59      | V <sub>SSB</sub>  | 72      |

| AD31     | 128     | NC         | 111     | <b>V</b> DD     | 84      | V <sub>SSB</sub>  | 82      |

NC = No Connect

RES\_DNC = Reserved\_DO NOT CONNECT.

#### LOGIC SYMBOL

Am53C974

8

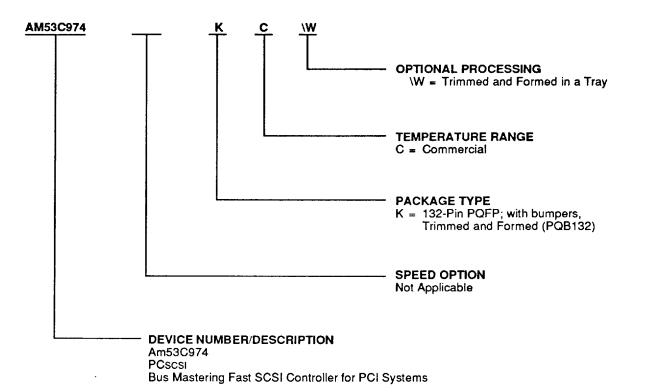

**ORDERING INFORMATION**

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |      |  |  |  |

|--------------------|------|--|--|--|

| AM53C974           | KC\W |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### PRELIMINARY

# DETAILED PIN DESCRIPTION PCI Bus Interface Signals

The Am53C974 is PCI compliant. The following pin descriptions have been taken from the PCI specification. For more details, refer to the PCI specification. Rev 2.0.

#### **Address and Data Pins**

## AD [31:00]

#### Address/Data

#### (Input/Output, Active High)

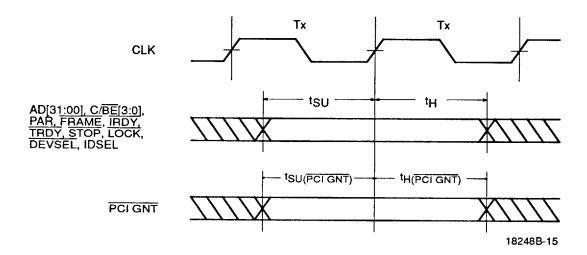

These signals are multiplexed on the same PCI pins. During the first clock of a transaction the AD [31:00] contains the physical byte address (32 bits). During the subsequent clocks AD [31:00] contains data. Little-endian byte ordering is used. AD [07:00] is defined as least significant byte and AD [31:24] is defined as the most significant byte.

When PCI RST is active, AD [31:00] are inputs for NAND tree testing.

## C/BE [3:0]

## Bus Command/Byte Enable

#### (Input/Output, Active Low)

These signals are multiplexed on the same PCI pins. During the address phase of the transaction, C/BE [3:0] define the bus command. During the data phase C/BE [3:0] are used as Byte Enables. The Byte Enables define which byte lanes carry meaningful data. C/BE0 applies to byte 0 and C/BE3 applies to byte 3.

When PCI RST is active, C/BE [3:0] are inputs for NAND tree testing.

#### **PAR**

#### **Parity**

#### (Input/Output, Active High)

Parity is even across AD[31:00] and C/BE[3:0]. Parity is generated and driven during Master Address Cycle, Memory Write, I/O Read, and Configuration Read cycles. Parity is checked during Slave Address Cycle, Memory Read, I/O Write, and Configuration Write cycles.

When PCI RST is active, PAR is an input for NAND tree testing.

#### Interface Control Pins

#### FRAME

#### Cycle Frame

#### (Input/Output, Active Low)

This signal is driven by the Am53C974 when it is the bus master to indicate the beginning and duration of the access. FRAME is asserted to indicate that a bus transaction is beginning. FRAME is asserted while data transfers continue. FRAME is deasserted when the transaction is in the final data phase.

When PCI RST is active, FRAME is an input for NAND tree testing.

#### TRDY

#### **Target Ready**

#### (Input/Output, Active Low)

When the Am53C974 is selected as a slave, it will drive (low) this signal to indicate its ability to complete the current data phase of the transaction. As a master, this signal is an input to the Am53C974 from the selected (slave) device.

TRDY is used in conjunction with IRDY to indicate completion of the data phase. The data phase is complete (on any clock) when both TRDY and IRDY are sampled when asserted. During a read transaction, TRDY is asserted when valid data is present on AD [31:00], while during a write transaction, TRDY asserted indicates the target is prepared to accept data. Wait cycles are inserted until both IRDY and TRDY are asserted together.

When PCI RST is active, TRDY is an input for NAND tree testing.

#### **IRDY**

#### **Initiator Ready**

#### (input/Output, Active Low)

When the Am53C974 is the initiator (master), it will drive (low) this signal to indicate its ability to complete the current data phase of the transaction. As a slave, this signal is an input to the Am53C974 from the initiating (master) device.

IRDY is used in conjunction with TRDY to indicate completion of the data phase. The data phase is complete (on any clock) when both IRDY and TRDY are sampled when asserted. During a read transaction, IRDY asserted indicates the master is prepared to accept data, while during a write transaction, IRDY is asserted to indicate that valid data is present on AD [31:00]. Wait cycles are inserted until both IRDY and TRDY are asserted together.

When PCI RST is active, IRDY is an input for NAND tree testing.

#### STOP

#### Stop

#### (Input/Output, Active Low)

In the slave role the Am53C974 drives the STOP signal to indicate to the bus master to stop the current transaction. In the bus master role the Am53C974 receives the STOP signal and stops the current transaction.

When PCI RST is active, STOP is an input for NAND tree testing.

10

#### **LOCK**

#### Lock

#### (input/Output, Active Low)

In the master role the Am53C974 drives the LOCK signal to indicate to the slave device that multiple transactions may be necessary to complete an operation. When LOCK is asserted, non-exclusive transactions may proceed. Control of LOCK is obtained under its own protocol in conjunction with GNT. In the slave role the Am53C974 receives the LOCK signal from the master.

When PCI RST is active, LOCK is an input for NAND tree testing.

#### Note:

In the current implementation, the Am53C974 as a master will never generate a LOCK. However, in slave role the chip will respond to a LOCK asserted by a master.

#### IDSEL

## Initialization Device Select (Input, Active High)

This signal is used as a chip select for the Am53C974 in lieu of the 24 address lines during configuration read and write transaction.

When PCI RST is active, IDSEL is an input for NAND tree testing.

#### DEVSEL

#### **Device Select**

### (Input/Output, Active Low)

This signal when actively driven by the Am53C974 as a slave device signals to the master device that it has decoded its address as the target of the current access. As an input it indicates whether any device on the bus has been selected.

When PCI RST is active, DEVSEL is an input for NAND tree testing.

#### **Arbitration Pins**

#### **PCI REQ**

#### **PCI Request**

#### (Output, Active Low)

This signal indicates to the arbiter that the Am53C974 desires use of the bus. This is a point to point signal. Every master has its own REQ which will be tri-stated after a power-up or a chip reset.

When PCI RST is active, PCI REQ is an input for NAND tree testing.

#### **PCI GNT**

#### **PCI Grant**

#### (Input, Active Low)

This signal indicates that the access to the bus has been granted to the Am53C974. This is a point to point signal. Every master has its own  $\overline{\text{GNT}}$ .

When PCI RST is active, PCI GNT is an input for NAND tree testing.

### **System Pins**

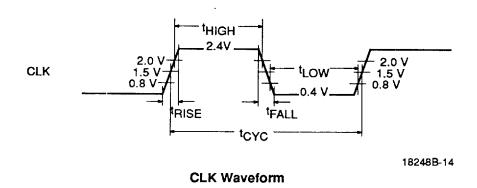

#### **CLK**

## Clock

#### (Input)

This signal provides timing for all the transactions on the PCI bus and all PCI devices on the bus including the Am53C974. All signals are sampled on the rising edge of CLK and all parameters are defined with respect to this edge. The Am53C974 operates at a frequency of up to 33 MHz.

When PCI RST is active, CLK is an input for NAND tree testing.

#### **PCI RST**

#### **PCI** Reset

#### (Input, Active Low)

This signal forces the Am53C974 Sequencer to a known state. All Three-State bi-directional signals are forced to a high impedance state and all Sustained Open Drain signals are allowed to float high. The Am53C974 arbiter will tristate PCI REQ if it is a master. This signal completely resets the SCSI core. PCI RST may be asynchronous to the CLK when asserted or deasserted. It is recommended that the deassertion be synchronous to guarantee clean and bounce free edge.

When PCI RST is active, NAND tree testing is enabled. All PCI interface pins are in input mode. The result of the NAND tree testing can be observed on the BUSY output (pin 62).

## **Error Reporting Pins**

#### PERR

#### **Parity Error**

#### (Input/Output, Active Low, Open Drain)

This signal may be pulsed by the Am53C974 when it detects a parity error during a data phase when its AD [31:00] and C/BE [3:0] lines are inputs.

When PCI RST is active, PERR is an input for NAND tree testing.

#### SERR

#### **System Error**

#### (Output, Active Low, Open Drain)

This signal may be pulsed by the Am53C974 for reporting address parity errors.

When PCI RST is active, SERR is an input for NAND tree testing.

Am53C974 11

## **Interrupt Request Pins**

#### INTA

Interrupt Request (Output, Active Low)

This signal combines the interrupt request from both the DMA engine and the SCSI core. The interrupt source can be determined by reading the DMA Status Register. It is cleared when the Status Register is read.

When PCI RST is active, INTA is an input for NAND tree testing.

## **SCSI Bus Interface Signals**

#### SCSI Bus Pins

### SD [7:0]

**SCSI Data**

(Input/Output, Active Low, Open Drain/Active Negation, Schmitt Trigger)

These pins are defined as bi-directional SCSI data bus.

#### SDP

**SCSI Data Parity**

(Input/Output, Active Low, Open Drain/Active Negation, Schmitt Trigger)

This pin is defined as bi-directional SCSI data parity.

#### MSG

Message

(Input, Active Low, Schmitt Trigger)

It is a Schmitt trigger input in the initiator mode.

#### $\overline{\mathbf{C}/\mathbf{D}}$

Command/Data

(Input, Schmitt Trigger)

It is a Schmitt trigger input in the initiator mode.

#### 1/0

Input/Output

(Input, Schmitt Trigger)

It is a Schmitt trigger input in the initiator mode.

#### **ATN**

Attention

(Output, Active Low)

This signal is a 48 mA output in the initiator mode. This signal will be asserted when the device detects a parity error; also, it can be asserted via certain commands.

#### **BSY**

Busy

(Input/Output, Active Low, Schmitt Trigger, Open Drain)

As a SCSI input signal it has a Schmitt trigger and as an output signal it has a 48 mA drive.

#### SEL

Select

(Input/Output, Active Low, Schmitt Trigger, Open Drain)

As a SCSI input signal it has a Schmitt trigger and as an output signal it has a 48 mA drive.

#### **SCSI RST**

#### Reset

(Input/Output, Active Low, Schmitt Trigger, Open Drain)

As a SCSI input signal it has a Schmitt trigger and as an output signal it has a 48 mA drive. The Reset SCSI command will cause the device to drive SCSI RST active for 25 ms - 40 ms depending on the CLK frequency and the conversion factor.

#### REQ

Request

(Input, Active Low, Schmitt Trigger)

This is a SCSI input signal with a Schmitt trigger in the initiator mode.

#### ACK

Acknowledge

(Output, Active Low, Open Drain/Active Negation) This is a SCSI output signal with a 48 mA drive in the initiator mode.

## **Power Management Signals**

#### **PWDN**

**Power Down Indicator**

(Input, Active High)

This signal, when asserted, sets the PWDN status bit in the DMA status register and sends an interrupt to the host.

#### BUSY

**SCSI Devices Busy**

(Output, Active Low)

This signal is logically equivalent to the SCSI bus signal BSY. It is duplicated so that external logic can be connected to monitor SCSI bus activity.

The results of the NAND tree testing can be observed on the BUSY pin. BUSY will reflect the state of the SCSI Bus Signal line BSY (pin 64) when PCIRST is deasserted.

#### Miscellaneous Signals

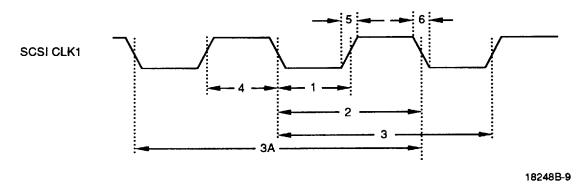

#### SCSI CLK1

## **SCSI Clock**

(Input)

The SCSI clock signal is used to generate all internal device timings. The maximum frequency of this input is 40 MHz and a minimum of 10 MHz is required to maintain the SCSI bus timings.

#### Note:

A 40 MHz clock must be supplied at this input to achieve 10 Mbyte/s Synchronous Fast SCSI transfers.

#### SCSI CLK2

### SCSI Clock

(Input)

This clock is required for a proper reset of the Am53C974. A minimum of 30 clock periods are needed to reset the chip properly. The clock value must be between 16 MHz and 40 MHz. For board layout convenience, SCSI CLK1 and SCSI CLK2 may be connected to a common clock source.

#### **RES DNC**

## Reserved\_DO NOT CONNECT

This pin (#116) is reserved for internal test logic. It MUST NOT BE CONNECTED to anything for proper chip operation.

#### **Power Supply Pins**

#### +5 V Power

(Input)

These inputs provide power necessary to operate the Am53C974. All V<sub>DD</sub> pins must be connected.

#### $V_{DDB}$

#### +5 V Power

(Input)

These inputs are for SCSI Buffers. These pins can be connected to the V<sub>DD</sub> pins.

#### $V_{DD3B}$

#### +5 V Power

(Input)

All V<sub>DD3B</sub> pins must be connected to a +5 V supply. These inputs are for PCI interface block.

#### V<sub>SS</sub>/V<sub>SSB</sub>/V<sub>SS3B</sub>

## Ground

(Input)

These inputs provide the necessary grounds to operate the Am53C974. The V<sub>SSBs</sub>, V<sub>SS3Bs</sub> and V<sub>SSs</sub> must be connected together.

#### **FUNCTIONAL DESCRIPTION**

This section covers the registers, commands, and operation of each of the three blocks: SCSI, DMA/FIFO, and PCI. The PCI Configuration space and the I/O address space are also covered.

#### I/O Address Map

The SCSI Core and DMA registers are addressed using the Base address register (10h) value. The SCSI registers occupy 16 double words and the DMA engine registers occupy 8 double word locations. The I/O address map is as follows:

| Start Offset | End Offset | Block Name    | Size      |

|--------------|------------|---------------|-----------|

| 0x0000       | 0x003F     | SCSI Core Reg | 16 DW/64B |

| 0x0040       | 0x005F     | PCI DMA CCB   | 8 DW/32B  |

The PCI configuration space, DMA and SCSI Core registers are described in the following sections.

#### **PCI** Interface

#### **Configuration Registers**

PCI configuration registers are used to determine which devices are in the system, and are also used to setup the configuration of those devices. Configuration registers are accessible only by PCI configuration cycles.

The Am53C974 supports the *Vendor ID, Device ID, Command and Status register* in the header, for PCI compliancy. Implementation of the other registers is optional depending on device functionality. Only the registers that are supported by the Am53C974 are described in this section. Please see the *PCI specification* for more detailed information on PCI registers.

Am53C974 supports the 64 byte predefined header portion (00h to 3Fh) of the 256 (100h) byte PCI configuration space. All of the device specific registers are in locations 64–255. All multi-byte numeric fields follow "little-endian" ordering. That is, lower addresses contain the least significant parts of the field. Table 1 shows the PCI configuration space header.

Table 1. The PCI Configuration Space Header

| 31         | 16            | 15              | 0                | Address<br>Offset |  |  |  |  |

|------------|---------------|-----------------|------------------|-------------------|--|--|--|--|

|            | Device ID     | Ven             | dor ID           | 00h               |  |  |  |  |

|            | Status        | Con             | nmand            | 04h               |  |  |  |  |

| Base Class | Sub Class     | Prog. If.       | Revision ID      | 08h               |  |  |  |  |

| BIST*      | Header Type*  | Latency Timer   | Cache Line Size* | 0Ch               |  |  |  |  |

|            | Base Address  |                 |                  |                   |  |  |  |  |

|            | Base Address* |                 |                  |                   |  |  |  |  |

|            | Base A        | Address*        |                  | 18h               |  |  |  |  |

|            | Base Address* |                 |                  |                   |  |  |  |  |

|            | Base Address* |                 |                  |                   |  |  |  |  |

|            | Base Address* |                 |                  |                   |  |  |  |  |

|            | Res           | erved*          |                  | 28h               |  |  |  |  |

|            | Res           | erved*          |                  | 2Ch               |  |  |  |  |

|            | Expansion ROI | M Base Address* |                  | 30h               |  |  |  |  |

|            | Resi          | erved*          |                  | 34h               |  |  |  |  |

|            | Res           | erved*          |                  | 38h               |  |  |  |  |

| Max_Lat*   | Min_Gnt*      | Interrupt Pin   | Interrupt Line   | 3Ch               |  |  |  |  |

| Reserved   | Reserved      | Reserved        | Reserved         | 40h**             |  |  |  |  |

| Reserved   | Reserved      | Reserved        | Reserved         | 44h**             |  |  |  |  |

| Reserved   | Reserved      | Reserved        | Reserved         | 48h**             |  |  |  |  |

| Reserved   | Reserved      | Reserved        | Reserved         | 4Ch**             |  |  |  |  |

<sup>\*</sup> Not Implemented on Am53C974. Writes to these locations will have no effect; reads from these locations will return '00h'.

<sup>\*\*</sup> Reserved for SCSI software.

### **Vendor ID Register**

## Address 00h (Read Only)

This register identifies the manufacturer Advanced Micro Devices, Inc. (AMD). The vendor ID is '1022h'.

#### **Device ID Register**

#### Address 02h (Read Only)

This register uniquely identifies this device within AMD's product line. The Am53C974 Device ID is '2020h'.

#### **Command Register**

## Address 04h (Read/Write)

The Command Register is used to control the gross functionality of the device. It controls the device's ability to generate and respond to PCI bus cycles. To logically disconnect the Am53C974 device from all PCI bus cycles except Configuration cycles, a value of zero should be written to this register.

#### Status Register

## Address 06h (Read/Write)

The Status register is used to read status information for the PCI bus. Reads to this register function normally, however writes function differently. On a write, bits may be reset (from 1 to 0), but not set.

#### **Revision ID Register**

### Address 08h (Read Only)

This register specifies the device specific revision number. The current value of this register is '00h'.

#### **Programming Interface Register**

#### Address 09h (Read Only)

This register identifies the programming interface of this device. The value in this register is 00h.

#### **Sub-Class Register**

#### Address OAh

#### (Read Only)

This register identifies this device as a SCSI Controller. The value in this register is '00h'.

#### **Base Class Register**

#### Address 0Bh

#### (Read Only)

This register identifies this device as a Mass Storage controller. The value in this register is '01h'.

#### **Latency Timer Register**

#### Address 0Dh

#### (Read Only)

The Latency Timer register is an 8-bit register specifying the maximum time the Am53C974 can continue with bus master transfers after the system arbiter has removed GNT. The time is measured in CLK cycles. The working copy of the timer will start counting down when the Am53C974 asserts FRAME for the first time during a bus mastership period.

The value for the Am53C974 Latency Timer register is '00h'.

#### **Base Address Register**

#### Address 10h

#### (Read/Write)

This register defines the I/O addresses used by the Am53C974. When this register is written, the register value identifies the I/O address occupied.

## Interrupt Line Register

## Address 3Ch (Read/Write)

The interrupt line register is used to communicate the routing of the interrupt. This register is written by the POST (Power-On Self Test) software as it initializes the PCI devices in the system.

#### Interrupt Pin Register

## Address 3Dh (Read Only)

This register identifies the interrupt pin used by Am53C974. This register will contain a value of '1' because the Am53C974 is using INTA.

#### **Reserved Register**

## Address 40h (Read/Write)

This register is a 32 bit read/write register which is currently undefined. Writes to this register will store data, and reads from this register reflect the data stored in this register.

### **Bus Cycle Definition**

The following table defines the PCI bus cycles:

| Cycle      | Bus Cycle Type            | Mode<br>Supported |  |  |

|------------|---------------------------|-------------------|--|--|

| C/BE [3:0] |                           |                   |  |  |

| 0000       | Interrupt ACK             | *                 |  |  |

| 0001       | Special Cycle             | *                 |  |  |

| 0010       | I/O Read                  | Slave             |  |  |

| 0011       | I/O Write                 | Slave             |  |  |

| 0100       | Reserved                  | •                 |  |  |

| 0101       | Reserved                  | •                 |  |  |

| 0110       | Memory Read               | Master            |  |  |

| 0111       | Memory Write              | Master            |  |  |

| 1000       | Reserved                  | •                 |  |  |

| 1001       | Reserved                  | *                 |  |  |

| 1010       | Config. Read              | Slave             |  |  |

| 1011       | Config. Write             | Slave             |  |  |

| 1100       | Memory Read Multiple      | •                 |  |  |

| 1101       | Dual Address Cycle *      |                   |  |  |

| 1110       | Mem. Read Line Master     |                   |  |  |

| 1111       | Memory Write & Invalidate | *                 |  |  |

<sup>\*</sup> These cycles are ignored by the Am53C974.

Refer to the technical manual for detailed bus cycle diagrams and explanations.

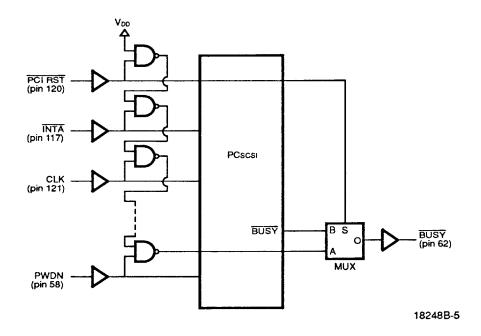

## **NAND Tree Testing**

The Am53C974 PCscsi controller provides a NAND tree test mode to allow checking connectivity to the device on a printed circuit board. The NAND tree is built on all PCI bus signals (see Figure 1 and Table 2).

The NAND tree testing is enabled by asserting PCI RST. All PCI signals will become inputs when PCI RST is asserted. The result of the NAND tree test can be observed on the BUSY pin.

)

Figure 1. NAND Tree

AMD

As shown in Figure 1, Pin 120 (PCI RST) is the first input to the NAND tree. Pin 117 (INTA) is the second input to the NAND tree, followed by pin 121 (CLK). All other PCI bus signals follow, counterclockwise, with pin 58

(PWDN) being the last. Pins labeled NC and all power supply pins are not part of the NAND tree. The complete list of pins connected to the NAND tree is shown in Table 2.

**Table 2. The NAND Tree Connection Pins**

| NAND<br>Tree |      |         | NAND<br>Tree |      |        | NAND<br>Tree |      |       |

|--------------|------|---------|--------------|------|--------|--------------|------|-------|

| Input #      | Pin# | Name    | Input #      | Pin# | Name   | Input #      | Pin# | Name  |

| 1            | 120  | PCI RST | 19           | 16   | AD20   | 37           | 39   | AD13  |

| 2            | 117  | ĪNTA    | 20           | 18   | AD19   | 38           | 40   | AD12  |

| 3            | 121  | CLK     | 21           | 19   | AD18   | 39           | 41   | AD11  |

| 4            | 124  | PCI GNT | 22           | 21   | AD17   | 40           | 42   | AD10  |

| 5            | 127  | PCI REQ | 23           | 22   | AD16   | 41           | 44   | AD9   |

| 6            | 128  | AD31    | 24           | 23   | C/BE2  | 42           | 45   | AD8   |

| 7            | 129  | AD30    | 25           | 24   | FRAME  | 43           | 47   | C/BE0 |

| 8            | 131  | AD29    | 26           | 25   | ĪRDY   | 44           | 48   | AD7   |

| 9            | 132  | AD28    | 27           | 26   | TRDY   | 45           | 49   | AD6   |

| 10           | 2    | AD27    | 28           | 27   | DEVSEL | 46           | 51   | AD5   |

| 11           | 3    | AD26    | 29           | 28   | STOP   | 47           | 52   | AD4   |

| 12           | 5    | AD25    | 30           | 29   | LOCK   | 48           | 53   | AD3   |

| 13           | 6    | AD24    | 31           | 31   | PERR   | 49           | 54   | AD2   |

| 14           | 7    | C/BE3   | 32           | 32   | SERR   | 50           | 56   | AD1   |

| 15           | 9    | IDSEL   | 33           | 34   | PAR    | 51           | 57   | AD0   |

| 16           | 12   | AD23    | 34           | 35   | C/BE1  | 52           | 58   | PWDN  |

| 17           | 13   | AD22    | 35           | 36   | AD15   |              |      |       |

| 18           | 15   | AD21    | 36           | 38   | AD14   |              |      |       |

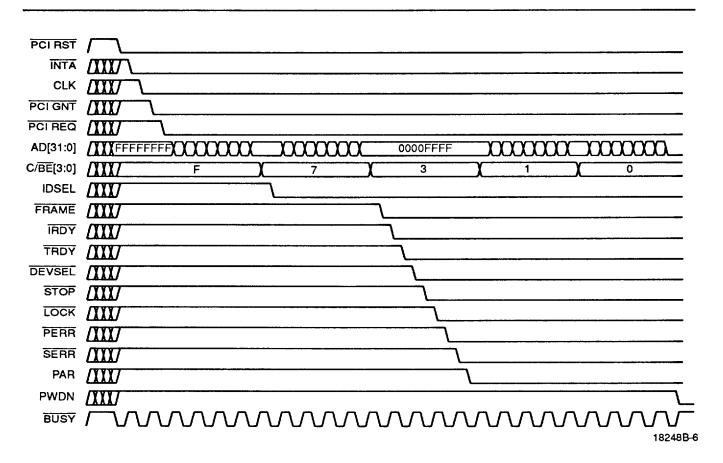

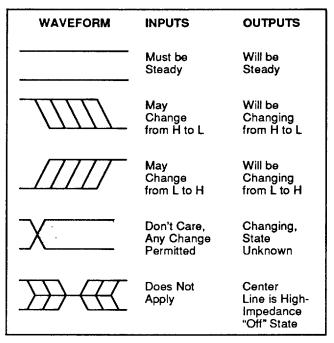

PCI RST must be asserted low to start a NAND tree test sequence. Initially, all NAND tree inputs except PCI RST should be driven high. This will result in a low output at the BUSY pin. If the NAND tree inputs are deasserted in the same order as they are connected to build the NAND tree, BUSY will toggle every time an additional input is deasserted. BUSY will change to a ONE, when INTA is deasserted and all other NAND tree inputs stay high. BUSY will toggle back to low, when CLK is additionally deasserted. The square wave will continue until all NAND tree inputs are deasserted. BUSY will be high, when all NAND tree inputs are deasserted (see Figure 2).

When testing is complete, deassert PCI RST to exit this test mode.

#### Note:

Some of the pins connected to the NAND tree are outputs in normal mode of operation. They must not be driven from an external source until the Am53C974 controller is configured for NAND tree testing.

Figure 2. NAND Tree Waveform

## AMD

## **DMA Engine and FIFOs**

#### **FIFOs**

The Am53C974 acts as a bridge between the PCI and SCSI buses. As the maximum data transfer rate on the PCI bus is a very high 132 Mbyte/s compared with the SCSI bus 10 Mbyte/s, buffering is required between the two buses. The buffering is provided by two FIFOs: 16-byte (16X8 bits) SCSI Core FIFO and an additional 96-byte (24X32 bits) DMA FIFO. These FIFOs provide a temporary storage for all command, data, status and message bytes as they are transferred between the 32-bit PCI bus and the 8-bit SCSI bus.

#### **DMA Registers**

The following is a description of the DMA register set or the DMA Channel Context Block (DMA CCB). The register addresses are referenced with the PCI configuration Base Register (10h) contents, represented by (B) in the Table 3.

The DMA registers control the DMA stage and transfer length and allow the programmer to specify a scatter-gather list that is stored in main memory. The MDL scatter-gather list will be described later. The three read-only working counter registers allow the system software and other driver layers to monitor the DMA transaction while it is in progress.

Table 3. The DMA Registers

| Register Acronym | Addr (Hex)                                        | Register Description                                          | Type |

|------------------|---------------------------------------------------|---------------------------------------------------------------|------|

| CMD (B)+40       |                                                   | Command (bits 31:8 reserved, bits 7:0 used)                   | R/W  |

| STC              | (B)+44                                            | Starting Transfer Count (bits 31:24 reserved, bits 23:0 used) | R/W  |

| SPA              | (B)+48 Starting Physical Address (bits 31:0 used) |                                                               | R/W  |

| WBC              | (B)+4C                                            | Working Byte Counter                                          | R    |

| WAC              | (B)+50                                            | Working Address Counter (bits 31:0 used)                      | R    |

| STATUS           | (B)+54                                            | Status Register (bits 31:8 reserved, bits 7:0 used)           | R    |

| SMDLA            | (B)+58                                            | Starting Memory Descriptor List (MDL) Address                 | R/W  |

| WMAC             | (B)+5C                                            | Working MDL Counter                                           | R    |

### Command Register (CMD)

The upper 3 bytes of Command register are reserved, the remaining (LSB) byte is defined as follows:

| Addre | ss (B)- | ⊦40h, L | F   | EAD/V    | VRITE    |      |      |  |

|-------|---------|---------|-----|----------|----------|------|------|--|

| 7     | 6       | 5       | 4   | 3        | 2        | 1    | 0    |  |

| DIR   | INTE_D  | INTE_P  | MDL | Reserved | Reserved | CMD1 | CMD0 |  |

#### DIR:

Data transfer direction bit.

#### INTE\_D:

DMA transfer active interrupt bit.

#### INTE P:

Page transfer active interrupt bit.

#### MDL:

Memory Descriptor List (MDL) SPA enable bit.

#### RESERVED:

Reserved for future expansion. The zero value must be written in these bits.

#### CMD1-0:

These two bits are encoded to represent three commands: IDLE, START, and ABORT.

| CMD1 | CMD0 | Command | Description                                                                                                                                                                                                       |

|------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | Х    | IDLE    | The DMA channel is inactive. Writes of these values are NOPs.                                                                                                                                                     |

| 1    | 0    | ABORT   | Terminate the current DMA transfer.                                                                                                                                                                               |

|      |      |         | Note: This is only valid after a START command is issued.                                                                                                                                                         |

| 1    | 1    | START   | Initiate a new DMA transfer.                                                                                                                                                                                      |

|      |      |         | This bit remains set throughout the entire DMA operation until bit 3 in the DMA status register is set.  Note: The software should issue a START command only after all other control bits have been initialized. |

#### Starting Transfer Count (STC) Address (B)+44h Read/Write

The STC register is a 24-bit read/write value that contains the number of bytes to be transferred. This register is not modified by the DMA transfer logic, and can be read by the software at any time. The system software can modify this register after the DMA transfer has been started.

#### Starting Physical Address (SPA) Address (B)+48h Read/Write

The SPA register is a 32-bit read/write address that is used as the starting address value for the DMA transfer. This register is not modified by the DMA transfer logic, and can be read by the software at any time. The system software can modify this register after the DMA transfer has been started.

#### Working Byte Counter (WBC) Address (B)+4Ch Read

The WBC register is a 24-bit read-only counter that is initialized to the value in the STC register when the transfer begins. It decrements by 1, 2, or 4 as data is sent to the PCI Bus by the controller. When the DMA transfer stops, a non zero value in this register indicates that the operation aborted earlier than expected (i.e. an error occurred). This register's intermediate values can be read by software in between DMA burst transactions.

#### Working Address Counter (WAC) Address (B)+50h Read

The WAC register is a 32-bit read-only address that is initialized to the value in the SPA register when the transfer begins. It increments as data is processed by the DMA channel, and will contain the address after the last access when the transfer terminates. This register's intermediate values can be read by software in between DMA burst transactions.

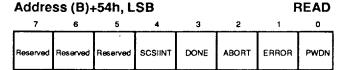

#### Status Register (Status)

The upper 3 bytes of the Status register are reserved, the remaining (LSB) byte is defined as follows:

The status Flags report the state of the DMA channel, any termination condition and SCSI interrupt.

#### RESERVED:

Reserved bits.

#### SCSIINT:

SCSI core interrupt bit.

#### DONE:

DMA transfer request termination bit.

DMA transfer request abort bit.

#### ERROR:

DMA transfer request termination with an error condition bit.

#### PWDN:

PWDN pin status bit.

#### Starting Memory Descriptor List Address (SMDLA) Address (B)+58H Read/Write

The SMDLA register is a 32-bit read/write address that is used as the starting address of the scatter-gather Memory Descriptor List. This register is not modified by the DMA transfer logic, and can be read by the software at any time. The system software can modify this register after the DMA transfer has been started.

#### Note:

The MDL start address must be word aligned since the hardware ignores non-zero values written to the two low address bits.

#### Working MDL Address Counter (WMAC) Address (B)+5CH Read

The WMAC register is a 32-bit read-only address that is initialized to the value in the SMDLA register when the transfer begins. It increments by 4 as new MDL entries are fetched by the DMA channel, and will contain the address after the last MDL read when the transfer terminates. This register's intermediate values can be read by software in between DMA burst transactions.

#### **DMA Scatter-Gather Mechanism**

The Am53C974 contains a scatter-gather translation mechanism which facilitates faster I/O data transfers. The mechanism uses a list of page frame addresses stored in system main memory that is called a Memory Descriptor List (MDL). The MDL page frame address allows a single SCSI transfer to read or write to non-contiquous address memory locations. The design eliminates the need for copying either the transfer data or the MDL locations.

20

#### **SCSI Core**

The SCSI core description covers a summary of the register definitions and the commands used by the SCSI core.

#### Registers

In the Am53C974, each SCSI register is mapped to a double-word address space, as shown in Table 4.

The actual register data occupies the least significant byte (LSB) of that particular double word address. Registers are accessed by specifying the base address (B) and the offset value specified below.

The Am53C974's base address is stored in register '10h.'

Table 4. SCSI Register Map

| Register<br>Acronym | Address (Hex.) | Register Description                                     | Operation  |

|---------------------|----------------|----------------------------------------------------------|------------|

| CTCREG              | (B)+00         | Current Transfer Count Register Low                      | Read       |

| STCREG              | (B)+00         | Start Transfer Count Register Low                        | Write      |

| CTCREG              | (B)+04         | Current Transfer Count Register Middle                   | Read       |

| STCREG              | (B)+04         | Start Transfer Count Register Middle                     | Write      |

| FFREG               | (B)+08         | FIFO Register                                            | Read/Write |

| CMDREG              | (B)+0C         | Command Register                                         | Read/Write |

| STATREG             | (B)+10         | Status Register                                          | Read       |

| SDIDREG             | (B)+10         | SCSI Destination ID Register                             | Write      |

| INSTREG             | (B)+14         | Interrupt Status Register                                | Read       |

| STIMREG             | (B)+14         | SCSI Timeout Register                                    | Write      |

| ISREG               | (B)+18         | Internal State Register                                  | Read       |

| STPREG              | (B)+18         | Synchronous Transfer Period Register                     | Write      |

| CFIREG              | (B)+1C         | Current FIFO/Internal State Register                     | Read       |

| SOFREG1             | (B)+1C         | Synchronous Offset Register                              | Write      |

| CNTLREG1            | (B)+20         | Control Register One                                     | Read/Write |

| CLKFREG             | (B)+24         | Clock Factor Register                                    | Write      |

| RES                 | (B)+28         | Reserved                                                 | Write      |

| CNTLREG2            | (B)+2C         | Control Register Two                                     | Read/Write |

| CNTLREG3            | (B)+30         | Control Register Three                                   | Read/Write |

| CNTLREG4            | (B)+34         | Control Register Four                                    | Read/Write |

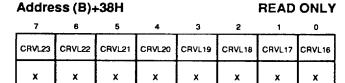

| CTCREG              | (B)+38         | Current Transfer Count Register High/Part Unique ID Code | Read       |

| STCREG              | (B)+38         | Start Transfer Count Register High                       | Write      |

| RES                 | (B)+3C         | Reserved                                                 | Write      |

Am53C974 21

#### **Register Descriptions**

The SCSI registers are described briefly in the following section. The bit map of the LSB reflects the default state after power-up or chip reset.

#### **Current Transfer Count Register (CTCREG)**

| Addre  | ss (B)⊦ | ⊦04H   |        |        |        | READ  | ONLY  |

|--------|---------|--------|--------|--------|--------|-------|-------|

| 7      | 6       | 5      | 4      | 3      | 2      | 1     | 0     |

| CRVL15 | CRVL14  | CRVL13 | CRVL12 | CRVL11 | CRVL10 | CRVL9 | CRVLB |

| x      | x       | ×      | х      | х      | x      | x     | х     |

| Addre | ss (B)- | ⊦00H  |       |       |       | READ  | ONLY  | , |

|-------|---------|-------|-------|-------|-------|-------|-------|---|

| 7     | 6       | 5     | 4     | 3     | 2     | 1     | 0     |   |

| CRVL7 | CRVL6   | CRVL5 | CRVL4 | CRVL3 | CRVL2 | CRVL1 | CRVL0 |   |

| x     | ×       | ×     | x     | x     | ×     | ×     | х     |   |

## CRVL 23:0 - Current Value 23:0

This is a three-byte register which decrements to keep track of the number of bytes transferred during a DMA transfer.

#### **Start Transfer Count Register (STCREG)**

| Addre  | ss (B)- | WRITE ONLY |        |        |        |        |        |

|--------|---------|------------|--------|--------|--------|--------|--------|

| 7      | 6       | 5          | 4      | 3      | 2      | 1      | 0      |

| STVL23 | STVL22  | STVL21     | STVL20 | STVL19 | STVL18 | STVL17 | STVL16 |

| ×      | ×       | x          | ×      | ×      | ×      | х      | x      |

| Addre  | ss (B)- | -04H       |        |        | ,      | VRITE  | ONLY   |

| Audie  | 33 (D)- | -0-411 |        |        | •      | AUHE  | ONLT  |

|--------|---------|--------|--------|--------|--------|-------|-------|

| 7      | 6       | 5      | 4      | 3      | 2      | 1     | 0     |

| STVL15 | STVL14  | STVL13 | STVL12 | STVL11 | STVL10 | STVL9 | STVL8 |

| х      | х       | x      | x      | x      | ×      | x     | x     |

| Address (B)+00H WRITE ONLY |       |       |       |       |       |       |       |  |

|----------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| 7                          | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

| STVL7                      | STVL6 | STVL5 | STVL4 | STVL3 | STVL2 | STVL1 | STVLO |  |

| x                          | х     | х     | х     | х     | х     | x     | х     |  |

#### STVL 23:0 - Start Value 23:0

This is a three-byte register which contains the number of bytes to be transferred during a DMA operation.

#### Note:

The Start Transfer Count register and the STC register of the DMA Engine should be programmed with the same value.

#### SCSI FIFO Register (FFREG)

| Addre | ss (B)+ | H80+ |     | READ/WRITE |     |     |     |

|-------|---------|------|-----|------------|-----|-----|-----|

| 7     | 6       | 5    | 4   | 3          | 2   | 1   | 0   |

| FF7   | FF6     | FF5  | FF4 | FF3        | FF2 | FF1 | FF0 |

| 0     | 0       | 0    | 0   | 0          | 0   | 0   | 0   |

#### FF 7:0 - FIFO 7:0

The bottom of the SCSI FIFO is mapped to this register.

#### SCSI Command Register (CMDREG)

| Ac | ddress (B)+ 0Ch           7         6         5         4         3           DMA         CMD6         CMD5         CMD4         CMD3 |      |      |      |      | READ/WRITE |      |      |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------------|------|------|--|

|    | 7                                                                                                                                     | 6    | 5    | 4    | 3    | 2          | 1    | 0    |  |

|    | MA .                                                                                                                                  | CMD6 | CMD5 | CMD4 | CMD3 | CMD2       | CMD1 | CMD0 |  |

|    | x                                                                                                                                     | х    | x    | х    | х    | ×          | х    | ×    |  |

Commands to the SCSI core are issued by writing to this register which is two bytes deep.

#### DMA - Direct Memory Access

This bit notifies the device that the command is a DMA instruction.

#### CMD 6:0 - Command 6:0

These command bits decode the commands that the device needs to perform.

## SCSI Status Register (STATREG)

| Addre | ss (B)- | ⊦10H |     |     |     |     | READ |  |

|-------|---------|------|-----|-----|-----|-----|------|--|

| 7     | 6       | 5    | 4   | 3   | 2   | 1   | 0    |  |

| INT   | ЮЕ      | PE   | CTZ | RES | MSG | C/D | νο   |  |

| 0     | 0       | 0    | 0   | х   | х   | x   | х    |  |

This read-only register contains flags to indicate the status and phase of the SCSI transactions.

22

#### INT - Interrupt

The INT bit is set when the device asserts the interrupt output.

#### IOE - Illegal Operation Error

The IOE bit is set when an illegal operation is attempted.

#### PE - Parity Error

The PE bit is set if any of the parity checking options are enabled and the device detects a parity error on bytes sent or received on the SCSI Bus.

#### CTZ - Count To Zero

The CTZ bit is set when the Current Transfer Count Register (CTCREG) has decremented to zero.

#### RES - Reserved

Reserved bit.

MSG – Message C/D – Command/Data I/O – Input/Output

The MSG, C/D and I/O bits indicate the phase of the SCSI bus.

#### SCSI Destination ID Register (SDIDREG)

## Address (B)+10H

WRITE ONLY

| 7   | 6   | 5   | 4   | 3   | 2    | 1    | 0    |

|-----|-----|-----|-----|-----|------|------|------|

| RES | RES | RES | RES | RES | DID2 | DID1 | DIDO |

| 0   | 0   | 0   | 0   | 0   | х    | x    | х    |

#### RES - Reserved

#### DID 2:0 - Destination ID 2:0

The DID 2:0 bits are the encoded SCSI ID of the device (0 thru 7) on the SCSI bus which needs to be selected or reselected.

#### Interrupt Status Register (INSTREG)

| Address (B)+14H | READ ONLY |

|-----------------|-----------|

|-----------------|-----------|

| 7    | 6    | 5   | 4  | 3  | 2     | 1   | 0   |

|------|------|-----|----|----|-------|-----|-----|

| SRST | ICMD | DIS | SA | so | RESEL | RES | RES |

| 0    | 0    | 0   | 0  | 0  | 0     | х   | х   |

The Interrupt Status Register (INSTREG) will indicate the reason for the interrupt.

#### SRST - SCSI Reset

The SRST bit will be set if a SCSI Reset is detected and SCSI reset reporting is enabled via the DISR (bit 6) of Control Register One (CNTLREG1).

#### ICMD - Invalid Command

The ICMD bit will be set if the device detects an illegal command code.

#### DIS - Disconnected

The DIS bit can be set in the Initiator mode when the device disconnects from the SCSI bus.

#### SR - Service Request

The SR bit can be set in the Initiator mode when another device on the SCSI bus has a service request.

#### SO - Successful Operation

The SO bit can be set in the Initiator mode when an operation has been successfully completed.

#### RESEL - Reselected

The RESEL bit is set at the end of the reselection phase indicating that the device has been reselected as an Initiator.

#### RES 1:0 - Reserved 1:0

Reserved bit.

#### SCSI Timeout Register (STIMREG)

#### Address (B)+14H

WRITE ONLY

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| STIM7 | STIM6 | STIM5 | STIM4 | STIM3 | STIM2 | STIM1 | STIMO |

| ×     | ×     | ×     | ×     | ×     | ×     | ×     | x     |

#### STIM 7:0 - SCSI Timer 7:0

This register determines how long the Initiator will wait for a response to a Selection before timing out.

#### Internal State Register (ISREG)

| Address (B)+18H READ ONLY |     |     |     |     |     |     |     |  |  |  |  |

|---------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| 7                         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

| RES                       | RES | RES | RES | SOF | 152 | IS1 | ISO |  |  |  |  |

| ×                         | x   | ×   | х   | 0   | 0   | 0   | 0   |  |  |  |  |

The Internal State Register (ISREG) tracks the progress of a sequence-type command.

#### RES - Reserved

#### SOF - Synchronous Offset Flag

The SOF is reset when the Synchronous Offset Register (SOFREG) has reached its maximum value.

#### IS 2:0 - Internal State 2:0

The IS 2:0 bits along with the Interrupt Status Register (INSTREG) indicates the status of the successfully completed intermediate operation.

#### Synchronous Transfer Period Register (STPREG)

#### Address (B)+18H WRITE 3 2 0 RES RES RES STP4 STP3 STP2 STP1 STPO X ¥ 0 n 1 0 1

#### RES - Reserved

#### STP 4:0 - Synchronous Transfer Period 4:0

These bits specify the synchronous transfer period or the number of clock cycles for each byte transferred in the synchronous mode.

#### **Current FIFO/Internal State Register (CFISREG)**

| Address (B)+ 1CH READ ONLY |     |     |     |     |     |     |     |  |  |  |

|----------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| 7                          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

| IS2                        | IS1 | ISO | CF4 | CF3 | CF2 | CF1 | CF0 |  |  |  |

| 0                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

This register has two fields, the Current FIFO field and the Internal State field.

#### IS 2:0 - Internal State 2:0

The Internal State Register (ISREG) tracks the progress of a sequence-type command.

#### CF 4:0 - Current FIFO 4:0

The CF 4:0 bits are the binary coded value of the number of bytes in the SCSI FIFO.

#### Synchronous Offset Register (SOFREG)

| Address (B)+ 1CH WRITE |      |      |      |     |     |     |     |  |  |  |

|------------------------|------|------|------|-----|-----|-----|-----|--|--|--|

| 7                      | 6    | 5    | 4    | 3   | 2   | 1   | 0   |  |  |  |

| RAD1                   | RAD0 | RAA1 | RAAO | SO3 | SO2 | SO1 | soo |  |  |  |

| 0                      | 0    | 0    | 0    | 0   | 0   | 0   | 0   |  |  |  |

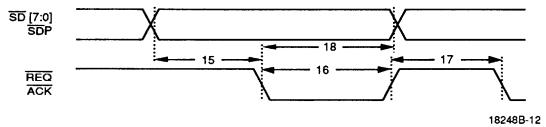

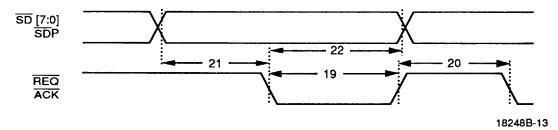

#### RAD 1:0 - REQ/ACK Deassertion Control

These bits may be programmed to control the deassertion delay of the REQ and ACK signals during synchronous transfers.

#### RAA 1:0 - REQ/ACK Assertion Control 1:0

These bits may be programmed to control the assertion delay of the REQ and ACK signals during synchronous transfers.

#### SO 3:0 - Synchronous Offset 3:0

The SO 3:0 bits are the binary coded value of the number of bytes that can be sent to (or received from) the SCSI bus without an ACK (or REQ) signal.

#### Control Register One (CNTLREG1)

| Addre | ss (B)+ | READ/WRITE |      |     |      |      |      |

|-------|---------|------------|------|-----|------|------|------|

| 7     | 6       | 5          | 4    | 3   | 2    | 1    | 0    |

| ЕТМ   | DISR    | RES        | PERE | RES | SID2 | SID1 | SIDO |

| 0     | 0       | 0          | 0    | 0   | x    | х    | ×    |

•

The Control Register 1 (CNTLREG1) sets up the device with various operating parameters.

#### ETM - Extended Timing Mode

Enabling this feature will increase the minimum setup time for data being transmitted on the SCSI bus.

#### DISR - Disable Interrupt on SCSI Reset

The DISR bit masks the reporting of the SCSI reset.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### PERE - Parity Error Reporting Enable

The PERE bit enables the checking and reporting of parity errors on incoming SCSI bytes during the information transfer phase.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### SID 2:0 - SCSI Device ID 2:0

The SID 2:0 bits specify the binary coded value of the device ID on the SCSI bus.

24

#### **PRELIMINARY**

#### Clock Factor Register (CLKFREG)

| Address (B)+24H WRITE |     |     |     |     |       |       |       |  |  |  |

|-----------------------|-----|-----|-----|-----|-------|-------|-------|--|--|--|

| 7                     | 6   | 5   | 4   | 3   | 2     | 1     | 0     |  |  |  |

| RES                   | RES | AES | RES | RES | CLKF2 | CLKF1 | CLKFO |  |  |  |

| ×                     | ×   | ×   | x   | x   | 0     | 1     | 0     |  |  |  |

The Clock Factor Register (CLKFREG) must be set to indicate the input frequency range of the device.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### CLKF 2:0 - Clock Factor 2:0

The CLKF 2:0 bits specify the binary coded value of the clock factor.

#### Reserved

#### Address (B)+28H WRITE RES RES RES RES RES RES RES RES х х x x X x x

#### RES - Reserved

This register is reserved. Its value must always be set to '00h'.

#### Control Register Two (CNTLREG2)

| 4 | Address (B)+2CH READ/WRITE |     |      |      |     |     |     |     |  |  |  |

|---|----------------------------|-----|------|------|-----|-----|-----|-----|--|--|--|

| _ | 7                          | 6   | 5    | 4    | 3   | 2   | 1   | 0   |  |  |  |

|   | RES                        | ENF | RES5 | RES4 | RES | RES | RES | RES |  |  |  |

|   | o                          | 0   | 0    | 0    | 0   | 0   | 0   | 0   |  |  |  |

The Control Register Two (CNTLREG2) sets up the device with various operating parameters.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### ENF - Enable Features

This bit activates the following product enhancements:

- The Current Transfer Count Register High ((B)+38H) will be enabled, extending the transfer counter from 16 to 24 bits to allow for larger transfers.

- Following a chip or power on reset, up until the point where the Current Transfer Count Register High ((B)+38H) is loaded with a value, it is possible to read the part-unique ID '12h' from this register.

■ The SCSI phase will be latched at the completion of each command by bits 2:0 in the Status Register (STATREG). When this bit is '0,' the Status Register (STATREG) will reflect real-time SCSI phases.

## RES5 - Reserved

This bit is internally tied low and is a read only bit.

#### RES4 - Reserved

This bit is internally tied low and is a read only bit.

#### RES 3:0 - Reserved 3:0

This bit is reserved and must always be set to '0.'

#### **Control Register Three (CNTLREG3)**

#### READ/WRITE Address (B)+30H 2 ADID CHK FAST-FASTCLK RES RES RES RES RES 0 0 ٥ ٥ 0 0 0

#### ADID CHK - Additional ID Check

Enables additional check on ID message during bus-initiated Select or Reselect with ATN.

#### RES - Reserved 6:5

This bit is reserved and must always be set to '0'.

#### FASTSCSI – Fast SCSI FASTCLK – Fast Clock

These bits configure the SCSI Core's state machine to support both Fast SCSI timings and SCSI-1 timings.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### RES - Reserved - READ-ONLY (Tied Low)

This reserved bit is internally tied low and is read-only.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### **Control Register Four (CNTLREG4)**

| Addre | ss (B)+ | READ/WRITE |     |                    |      |     |     |

|-------|---------|------------|-----|--------------------|------|-----|-----|

| 7     | 6       | 5          | 4   | 3                  | 2    | 1   | 0   |

| GE1   | GE0     | PWD        | RES | RES (R)<br>RAE (W) | RADE | RES | RES |

| 0     | 0       | 0          | х   | 0                  | 0    | x   | x   |

This register is used to control several AMD proprietary features implemented in the SCSI Core. At power up, this register will show a '0' value on all bits except bit 4.

Am53C974

25

GE1:0 - GLITCH EATER 1:0

The GLITCH EATER circuitry has been implemented on REQ, ACK, and DATA lines and are controlled by bits 7 and 6. The valid signal window may be adjusted by setting the bits in the combinations listed below.

| GE1 | GE0 | Valid Signal<br>Window |

|-----|-----|------------------------|

| 0   | 0   | 12 ns                  |

| 1   | 0   | 25 ns                  |

| 0   | 1   | 35 ns                  |

| 1   | 1   | 0 ns                   |

#### PWD - Power-Down Feature

Setting this bit to '1' turns off the input buffers on all the SCSI bus signal lines.

#### RES - Reserved

This bit is reserved for internal use.

#### RES - Reserved (Read Only)

This bit is reserved for internal use.

#### RAE - (Write Only) - Active Negation Control RADE - Active Negation Control

RAE and RADE Bits 2 and 3 control the Active Negation Drivers which may be enabled on REQ, ACK, or DATA lines.

The programming options for this feature are as follows:

| RAE | RADE | Function Selected                    |

|-----|------|--------------------------------------|

| 0   | 0    | Active Negation Disabled             |

| 1   | 0    | Active Negation on REQ and ACK only  |

| X   | 1    | Active Negation on REQ, ACK and DATA |

#### RES - Reserved

This bit is reserved for internal use.

#### RES - Reserved

This bit is reserved and must always be set to '0'.

#### Reserved

| Addre | V   | WRITE |     |     |     |     |     |  |

|-------|-----|-------|-----|-----|-----|-----|-----|--|

| 7     | 6   | 5     | 4   | 3   | 2   | 1   | 0   |  |

| RES   | RES | RES   | RES | RES | RES | RES | RES |  |

| 0     | 0   | 0     | 0   | 0   | 0   | 0   | 0   |  |

#### RES - Reserved

This register is reserved. Its value must always be set to '00h'.

#### Part-Unique ID Register ((B)+38H) Read Only

This register extends the transfer counter from 16 to 24 bits and is only enabled when the ENF bit is set (bit 6, Control Register Two).

This register is also used to store the part-unique ID code for the SCSI. This information may be accessed when all of the following are true:

- 1. A power up or chip reset has taken place

- 2. A value has not been loaded into this register

26

### **SCSI Commands**

The following is a summary of the SCSI commands supported by the SCSI Core. For more details on implementation, refer to the Am53C974 Technical Manual.

Table 5. Summary of Commands

|                                  | Co<br>(He           |             |

|----------------------------------|---------------------|-------------|

| Command                          | Non-<br>DMA<br>Mode | DMA<br>Mode |

| Initiator Commands               |                     |             |

| Information Transfer             | 10                  | 90          |

| Initiator Command Complete Steps | 11                  | 91          |

| Message Accepted                 | 12                  | _           |

| Transfer Pad Bytes               | _                   | 98          |

| Set ATN*                         | 1A                  | _           |

| Reset ATN*                       | 1B                  | -           |

| Idle State Commands              |                     |             |

| Select without ATN Steps         | 41                  | C1          |

| Select with ATN Steps            | 42                  | C2          |

| Select with ATN and Stop Steps   | 43                  | СЗ          |

| Enable Selection/Reselection*    | 44                  | C4          |

| Disable Selection/Reselection    | 45                  | _           |

| Select with ATN3 Steps           | 46                  | C6          |

| General Commands                 |                     |             |

| No Operation*                    | 00                  | 80          |

| Clear FIFO*                      | 01                  | -           |

| Reset Device*                    | 02                  | _           |

| Reset SCSI Bus**                 | 03                  | -           |

#### Notes:

<sup>\*</sup> These commands do not generate interrupt.

<sup>\*\*</sup> An interrupt is generated when SCSI bus reset interrupt reporting is not disabled (see Control Register1/DISR bit6).

#### 68E D ■ 0257525 0045396 264 ■ AMDL PRELIMINARY

#### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature ......  $-65^{\circ}$ C to  $+150^{\circ}$ C Ambient Temperature Under Bias .....  $-55^{\circ}$ C to  $+125^{\circ}$ C  $V_{DD}$  ..... -0.5 V to +7.0 V DC Voltage Applied to Any Pin ..... -0.5 to  $(V_{DD}$  +0.5) V Input Static Discharge Protection .... 2K V pin-to-pin (Human body model: 100 pF at 1.5K  $\Omega$ )

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

Commercial (C) Devices

Ambient Temperature (T<sub>A</sub>) ...... 0°C to +70°C

Supply Voltage (V<sub>DD</sub>) ..... 4.75 V to 5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

28

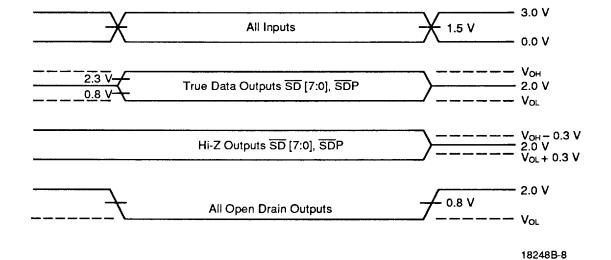

# DC CHARACTERISTICS over COMMERCIAL operating range unless otherwise specified